Stored data format is supported by HRPTReader.

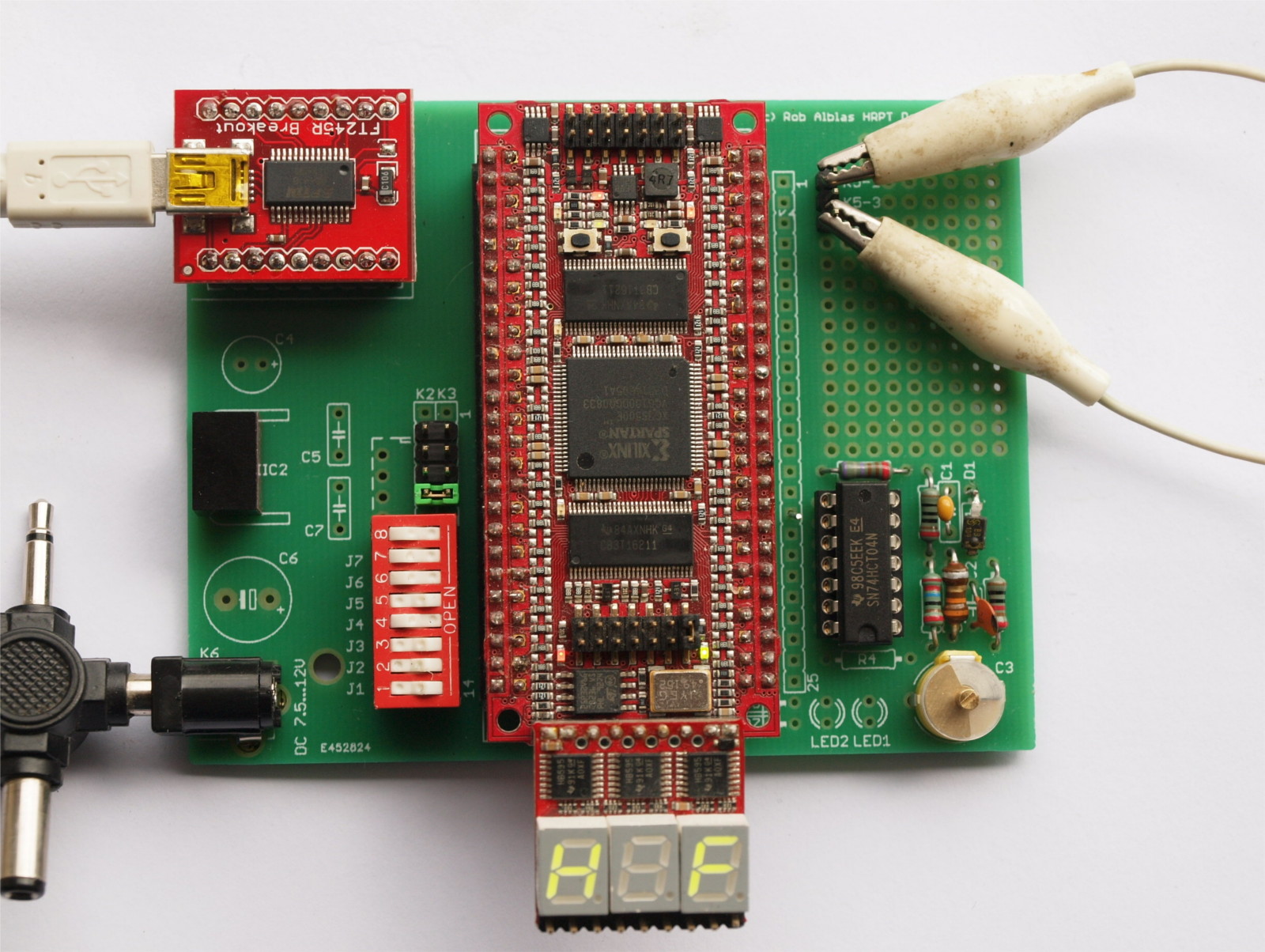

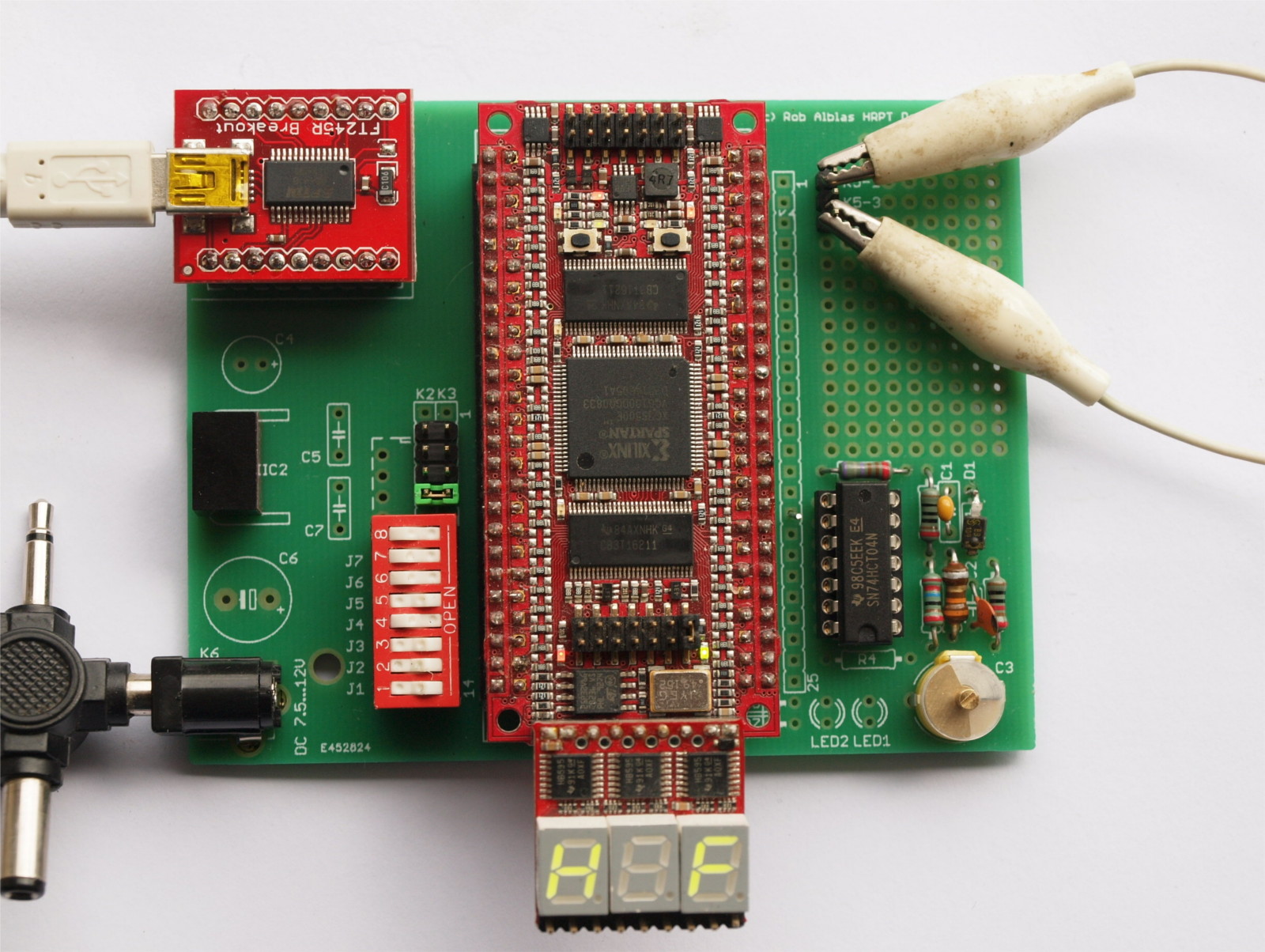

GODIL has following power-pins:

For C and L around VCO several values can be used: For 10.6 MHz:

| GODIL Pin | C25 | A24 | C23 | A22 | C25 | A24 | C23 | A22 | comment | |

|---|---|---|---|---|---|---|---|---|---|---|

| Type | J1 | J2 | J3 | J4 | val | val | val | val | ||

| HRPT | x | x | x | x | 0 | 0 | 0 | 0 | ||

| CHRPT | - | x | x | x | 1 | 0 | 0 | 0 | not active | |

| MHRPT1 | x | - | x | x | 0 | 1 | 0 | 0 | not active | |

| MHRPT2 | - | - | x | x | 1 | 1 | 0 | 0 | ||

| METOP | x | x | - | x | 0 | 0 | 1 | 0 | ||

| FY3A,B | x | - | - | x | 0 | 1 | 1 | 0 | ||

| FY3C | - | x | - | x | 1 | 0 | 1 | 0 | ||

| IQ record | - | - | - | x | 1 | 1 | 1 | 0 | ||

| set by SW | * | * | * | - | * | * | * | 1 | ||

| Pin | C17 | A16 | C17 | A16 | ||

|---|---|---|---|---|---|---|

| Freq MHz | J9 | J10 | val | val | Note | |

| 10.646 MHz | x | x | 0 | 0 | don't use for 2017+ firmware! | |

| 21.292 MHz | - | x | 1 | 0 | Use this for any firmware | |

| 42.584 MHz | x | - | 0 | 1 | Use this for any firmware | |

| 10.646 MHz | - | - | 1 | 1 | don't use for 2017+ firmware! | |

| Pin | C17 | A16 | C17 | A16 | ||

|---|---|---|---|---|---|---|

| Freq MHz | J9 | J10 | val | val | Note | |

| --- | x | x | 0 | 0 | don't use! | |

| 20.000 MHz | - | x | 1 | 0 | May be used for any firmare | |

| 40.000 MHz | x | - | 0 | 1 | May be used for any firmare | |

| --- | - | - | 1 | 1 | don't use! | |

| function | Pin | jumper | set | val |

|---|---|---|---|---|

| enable integrator | C21 | J5 | - | 1 |

| disable integrator | C21 | J5 | x | 0 |

| invert input | A20 | J6 | x | 0 |

| normal input | A20 | J6 | - | 1 |

| middle display: quality input sig | C19 | J7 | x | 0 |

| middle display: lock state PLL | C19 | J7 | - | 1 |

| function | pin | comment |

|---|---|---|

| data clock | B24 | These are EXOR-ed to phd |

| VCO clock | B22 | |

| datachange eyecenter | B20 | pulse width=1 VCO clockcycle |

| out-sync | D25 | lockindication 2-colour-LED |

| in-sync | D23 | |

| 1=VCO too high | D21 | VCO lock indication |

| 1=VCO too low | D19 | |

| 1=buffer overflow | D11 |

| K4: right con | GODIL con | FPGA con | name | - | left con/dipsw | GODIL con | FPGA con | name |

|---|---|---|---|---|---|---|---|---|

| 1 | D1 | P91 | Generator out (I) | C1 | P26 | usb_data[0] | ||

| 2 | B2 | P12 | Generator out (Q) | A2 | P15 | usb_data[1] | ||

| 3 | D3 | P11 | decoder in (I) | C3 | P16 | usb_data[2] | ||

| 4 | B4 | P10 | decoder in (Q) | A4 | P95 | usb_data[3] | ||

| 5 | D5 | P9 | scl | C5 | P18 | usb_data[4] | ||

| 6 | B6 | P90 | diseqc_do[0] | A6 | P17 | usb_data[5] | ||

| 7 | D7 | P5 | sda | C7 | P94 | usb_data[6] | ||

| 8 | B8 | P4 | diseqc_do[1] | A8 | P22 | usb_data[7] | ||

| 9 | D9 | P2 | TX RS232 | C9 | P23 | usb_rd | ||

| 10 | B10 | P3 | - | A10 | P33 | usb_wr | ||

| 11 | D11 | P98 | ovf | C11 | P32 | usb_txe | ||

| 12 | B12 | P92 | - | A12 | P34 | usb_rxf | ||

| 13 | D13 | P88 | clkb: VCO | C13 | P38 | - | ||

| 14 | B14 | P85 | sd_sample[0] | A14 | P40 | - | ||

| 15 | D15 | P79 | phd | C15 | P41 | - | ||

| 16 | B16 | P78 | sd_sample[1] | A16 | P36 | sel_vco[1] | ||

| 17 | D17 | P83 | clka: VCO | C17 | P35 | sel_vco[0] | ||

| 18 | B18 | P84 | - | D8 | A18 | P53 | sel_clk | |

| 19 | D19 | P86 | ool[0] | D7 | C19 | P54 | dispmode | |

| 20 | B20 | P71 | errpls | D6 | A20 | P57 | dinv_not | |

| 21 | D21 | P70 | ool[1] | D5 | C21 | P58 | ena_bitintegr | |

| 22 | B22 | P68 | ckvco | D4 | A22 | P60 | dectype sw/manual | |

| 23 | D23 | P67 | rg_syncled[0] | D3 | C23 | P61 | dectype[2] | |

| 24 | B24 | P66 | ckdat | D2 | A24 | P62 | dectype[1] | |

| 25 | D25 | P65 | rg_syncled[1] | D1 | C25 | P63 | dectype[0] | |

| GODIL con | FPGA con | name |

|---|---|---|

| ? | sclk | P44 |

| ? | ser | P50 |

| ? | rclk | P27 |

| FPGA con | name |

|---|---|

| clkgen | P89 |

| rled | P43 |

| gled | P25 |

(To continue)

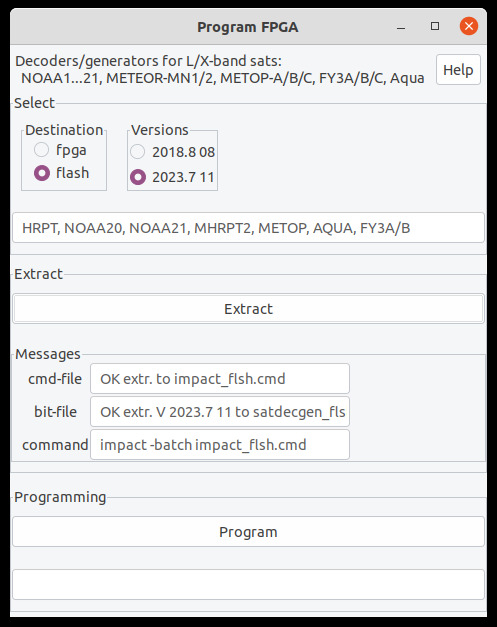

After downloading and installing you should now have a tool called impact(.exe), located at: (location may differ)

Instead of programming the flash you can also program directly into the FPGA. The flash is then not changed; after a power-cycle the original program in flash is loaded. In this way it possible to try a new program before "definitely" load it into flash.

Bit files and command files are available here.

For Windows, if no search path is defined to 'impact', an option can be added

to define full path to the impact tool.

This needs to be defined in the startup-icon, at 'property', e.g.:

ld_fpga C:\Xilinx\labtools\ISE\impact.exe

Newest load contains:

| frame | satellite | input speed | coding | output speed | status |

|---|---|---|---|---|---|

| HRPT | NOAA19, 18 etc. | 1.3308 Mb/s | Manchester | 0.6654 Mb/s | OK |

| AHRPT | NOAA20 | 2x 15 Mb/s | Viterbi 1/2 | 15 Mb/s | not tested with real data yet

generator gives METOP-like data |

| AHRPT | NOAA21 | 2x 25 Mb/s | Viterbi 1/2 | 25 Mb/s | not tested with real data yet

generator gives METOP-like data |

| AHRPT | Meteor MN2 * | 1.3308 Mb/s | Manchester | 0.6654 Mb/s | OK |

| AHRPT | METOP | 2x 2.333 Mb/s | Viterbi 3/4 | 3.5 Mb/s | OK |

| AHRPT | FY3AB | 2x 2.8 Mb/s | Viterbi 3/4 | 4.2 Mb/s | OK |

| AHRPT? | Aqua | 2x 7.5 Mb/s | none | 15 Mb/s | not tested with real data yet

generator gives METOP-like data needs half bit shift on Q to do SQPSK |

Version 10, 2022.01:

| Versions | Date | Content | clock | loader Linux | loader Windows |

|---|---|---|---|---|---|

| 01 | 2017.8 | decoders, generators, DiSEqC (needs trimming of vco between sat-types) | VCO ~ 21.29 MHz | ldfpga_1578a.tgz | setup_ldfpga_1578a.exe |

| 05 | 2017.8 | decoders, generators, DiSEqC; more accurate deriving base clock | VCO 21.00 MHz | ||

| 07 | 2018.2 | decoders, generators, DiSEqC; very accurate deriving base clock | VCO / VCXO 20.000000, 40.000000, 80.000000 MHz | ||

| 08 | 2018.8 | better metop/fengyun generator (gives test pictures) higher display update rate | VCO / VCXO 20.000000, 40.000000, 80.000000 MHz | ||

| 10 | 2022.01 | Added NOAA20 decoder/generator (generator currently generates metop@noaa20 rate) Added Aqua decoder/generator (generator currently generates metop@noaa20 rate) Added UART connection (38.4 kb/s) to use with receiver, to enable frequency set from PC | VCO / VCXO 20.000000, 40.000000, 120.000000 MHz | ||

| 11 | 2023.07 | Added NOAA21 decoder/generator (generator currently generates metop@noaa21 rate) Corrected Aqua: OQPSK, IQ-rotate if out-sync show syncstate aqua on LED display | VCXO 20.000000, 40.000000, 120.000000 MHz | ldfpga_11072023.tgz (29-7-2023) | setup_ldfpga_11072023.exe (29-7-2023) |

| 12 | 2024.01 | Added NOAA21 decoder/generator (generator currently generates metop@noaa21 rate); OLED display driver | VCXO 20.000000, 40.000000, 120.000000 MHz | ||

| 13 | 2025.05 | Added NOAA21 decoder/generator (generator currently generates metop@noaa21 rate); OLED display driver Fixed autotune | VCXO 20.000000, 40.000000, 120.000000 MHz | ldfpga64.tgz (30-05-2025) | setup_ldfpga.exe (30-05-2025) |

| 2.0 | Needed DLL-libs | setup_gtk20dll.exe (2.6 Mbyte) | for all releases, needed to download/install just one time |

| Version | Content | Bit-file | Command file | Comment |

|---|---|---|---|---|

| V2_1 (2015.01) | Flash load | nfm_hrptdecgen_2015_01.mcs | impact_flsh_2015_01.cmd | To load into flash |

| V2_1 (2015.01) | direct load | nfm_hrptdecgen_2015_01.bit | impact_fpga_2015_01.cmd | To load into FPGA directly, needs to be done each time after power-up (flash content not changed) |

| Version | Content | Bit-file | Command file | Comment |

|---|---|---|---|---|

| V0_1 (2017.04) | Flash load | hcmMFdecgen_flsh_01042017.mcs | impact_hcmMFdecgen_flsh_01042017.cmd | To load into flash |

| V0_1 (2017.04) | direct load | hcmMFdecgen_fpga_01042017.bit | impact_hcmMFdecgen_fpga_01042017.cmd | To load into FPGA directly, needs to be done each time after power-up (flash content not changed) |

| Version | Content | Bit-file | Comment | |

|---|---|---|---|---|

| V1_0 (2011.03) | Flash load | nfm_hrptdecgen.mcs | To load into flash | |

| direct load | nfm_hrptdecgen.bit | To load into FPGA directly, needs to be done each time after power-up | ||

| pinning | nfm_hrptdecgen_v10.xcf | |||

| V0_7 (2011.03) | direct load | nfm_hrptdecgen_v07.bit | To load into FPGA directly, needs to be done each time after power-up | |

| Flash load | nfm_hrptdecgen_v07.mcs | To load into flash | ||

| V0_5 (2011.02) | direct load | nfm_hrptdecgen_v05.bit | To load into FPGA directly, needs to be done each time after power-up | |

| Flash load | nfm_hrptdecgen_v05.mcs | To load into flash | ||

| pinning | nfm_hrptdecgen_v05.xcf |